No. of Printed Pages: 4

BIELE-012

P.T.O.

## B.Tech. - VIEP - ELECTRONICS AND COMMUNICATION ENGINEERING (BTECVI)

## 00629

BIELE-012

## Term-End Examination December, 2017

## **BIELE-012: ELECTRONIC SWITCHING CIRCUITS**

| Ti                                                                                                                                          | me : 3_ | hours Maximum Marks:                                                                                                                                     | Maximum Marks : 70 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Note: Attempt any seven questions. All questions carry equal marks. Assume missing data, if any. Use of scientific calculator is permitted. |         |                                                                                                                                                          |                    |  |

| 1.                                                                                                                                          | (a)     | Distinguish between Combinational and Sequential circuits.                                                                                               | 3                  |  |

|                                                                                                                                             | (b)     | Differentiate between Latch and Register.<br>Explain using timing diagram.                                                                               | 3                  |  |

|                                                                                                                                             | (c)     | Explain the operation of SR flip-flop and mention its excitation table.                                                                                  | 4                  |  |

| 2.                                                                                                                                          | (a)     | Explain the operation of JK flip-flop. How does a JK flip-flop differ from an SR flip-flop in its operation? What is its advantage over an SR flip-flop? | 5                  |  |

|                                                                                                                                             | (b)     | An 8-bit D/A converter has a step size of 20 mV. Determine the full-scale output and percentage resolution.                                              | 5                  |  |

1

- 3. A long input sequence enters a one-input one-output synchronous sequential circuit that is required to produce an output symbol z=1. Whenever the sequence 1111 occurs, overlapping sequences are accepted. For example, if the input sequence is 010111111..., the required output sequence is 00000011....

- (a) Draw a state diagram.

- (b) Select an assignment and show the excitation and output tables.

- (c) Write down the excitation functions for SR flip-flops and draw the corresponding logic diagram.

10

8

4. (a) Design a modulo-8 counter that counts in the way specified in the table shown below, using JK flip-flop:

| Decimal | Gray Code |

|---------|-----------|

| 0       | 000       |

| 1       | 001       |

| 2       | 011       |

| 3       | 010       |

| 4       | 110       |

| 5       | 111       |

| 6       | 101       |

| 7       | 100       |

- (b) Differentiate between synchronous and asynchronous sequential circuits.

- 2

5

- **5.** (a) What is hazard in a logic circuit? Classify the hazards in logic circuits.

- (b) How do you design a hazard-free circuit?

Explain with suitable example. 5

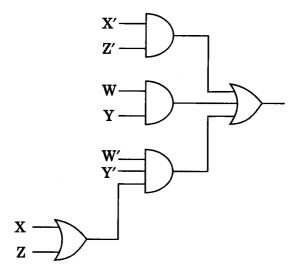

- **6.** Analyze the circuit as shown in Figure 1 for static hazards. Redesign it to make it static hazard-free. 10

Figure 1

- 7. (a) Explain the operation of Master-Slave JK flip-flop with set and clear inputs.

- (b) Explain the working principle of a negative edge-triggered D-flip-flop.

BIELE-012

5

5

| 8.  | (a)              | Describe the symmetric functions and enlist all the properties of symmetric functions.  5                          |  |  |  |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

|     | (b)              | What do you mean by Contact Network?  Explain the synthesis process of a contact network with suitable example.  5 |  |  |  |

| 9.  | Briefly describe |                                                                                                                    |  |  |  |

|     | (a)              | how the architecture of an asynchronous up-counter differs from that of a down-counter.                            |  |  |  |

|     | (b)              | how the architecture of a ring counter differs from that of a shift counter.                                       |  |  |  |

| 10. | Write<br>follow  | *                                                                                                                  |  |  |  |

|     | (a)              | Glitches                                                                                                           |  |  |  |

|     | (b)              | Dynamic Hazards                                                                                                    |  |  |  |

|     | (c)              | Pulse Mode Circuits                                                                                                |  |  |  |

|     | (d)              | Sequence Detector and Sequence<br>Generator                                                                        |  |  |  |

|     |                  |                                                                                                                    |  |  |  |